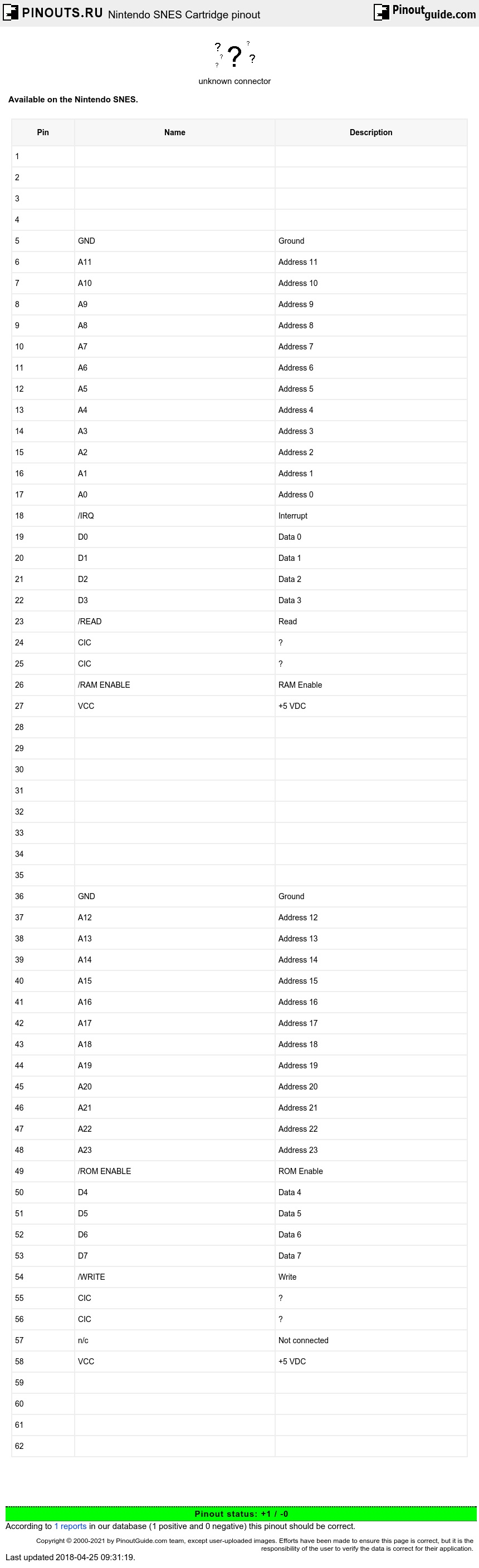

| Pin | Name | Description |

|---|---|---|

| 1 | MASTER_CLOCK | 21.477MHz Clock |

| 2 | EXPAND | Expansion Port Pad |

| 3 | PA6 | Bus B Address 7 |

| 4 | /PARD | Bus B Read |

| 5 | GND | Ground |

| 6 | A11 | Bus A Address 11 |

| 7 | A10 | Bus A Address 10 |

| 8 | A9 | Bus A Address 9 |

| 9 | A8 | Bus A Address 8 |

| 10 | A7 | Bus A Address 7 |

| 11 | A6 | Bus A Address 6 |

| 12 | A5 | Bus A Address 5 |

| 13 | A4 | Bus A Address 4 |

| 14 | A3 | Bus A Address 3 |

| 15 | A2 | Bus A Address 2 |

| 16 | A1 | Bus A Address 1 |

| 17 | A0 | Bus A Address 0 |

| 18 | /IRQ | Interrupt |

| 19 | D0 | Data 0 |

| 20 | D1 | Data 1 |

| 21 | D2 | Data 2 |

| 22 | D3 | Data 3 |

| 23 | /RD | Bus A Read |

| 24 | CIC_DOUT | CIC Data Out |

| 25 | CIC_DIN1 | CIC Data In 1 |

| 26 | /RESET | Reset |

| 27 | VCC | +5V DC |

| 28 | PA0 | Bus B Address 0 |

| 29 | PA2 | Bus B Address 2 |

| 30 | PA4 | Bus B Address 4 |

| 31 | AUDIO_L | Left Audio Input |

| 32 | /WRAM | WRAM Access |

| 33 | REFRESH | DRAM Refresh |

| 34 | PA7 | Bus B Address 7 |

| 35 | /PAWR | Bus B Write |

| 36 | GND | Ground |

| 37 | A12 | Bus A Address 12 |

| 38 | A13 | Bus A Address 13 |

| 39 | A14 | Bus A Address 14 |

| 40 | A15 | Bus A Address 15 |

| 41 | A16 | Bus A Address 16 |

| 42 | A17 | Bus A Address 17 |

| 43 | A18 | Bus A Address 18 |

| 44 | A19 | Bus A Address 19 |

| 45 | A20 | Bus A Address 20 |

| 46 | A21 | Bus A Address 21 |

| 47 | A22 | Bus A Address 22 |

| 48 | A23 | Bus A Address 23 |

| 49 | /ROMSEL | ROM Enable |

| 50 | D4 | Data 4 |

| 51 | D5 | Data 5 |

| 52 | D6 | Data 6 |

| 53 | D7 | Data 7 |

| 54 | /WR | Bus A Write |

| 55 | CIC_DIN0 | CIC Data In 0 |

| 56 | CIC_CLOCK | CIC Clock |

| 57 | CPU_CLOCK | CPU Clock |

| 58 | VCC | +5V DC |

| 59 | PA1 | Bus B Address 1 |

| 60 | PA3 | Bus B Address 3 |

| 61 | PA5 | Bus B Address 5 |

| 62 | AUDIO_R | Right Audio Input |

+------------------------------//------------------------------+ | 32 33 34 35 | 36 37 38 39 40 // 53 55 56 57 58 | 59 60 61 62 | | 01 02 03 04 | 05 06 07 08 09 // 22 24 25 26 27 | 28 29 30 31 | +------------------------------//------------------------------+

correct

correct incorrect

incorrect