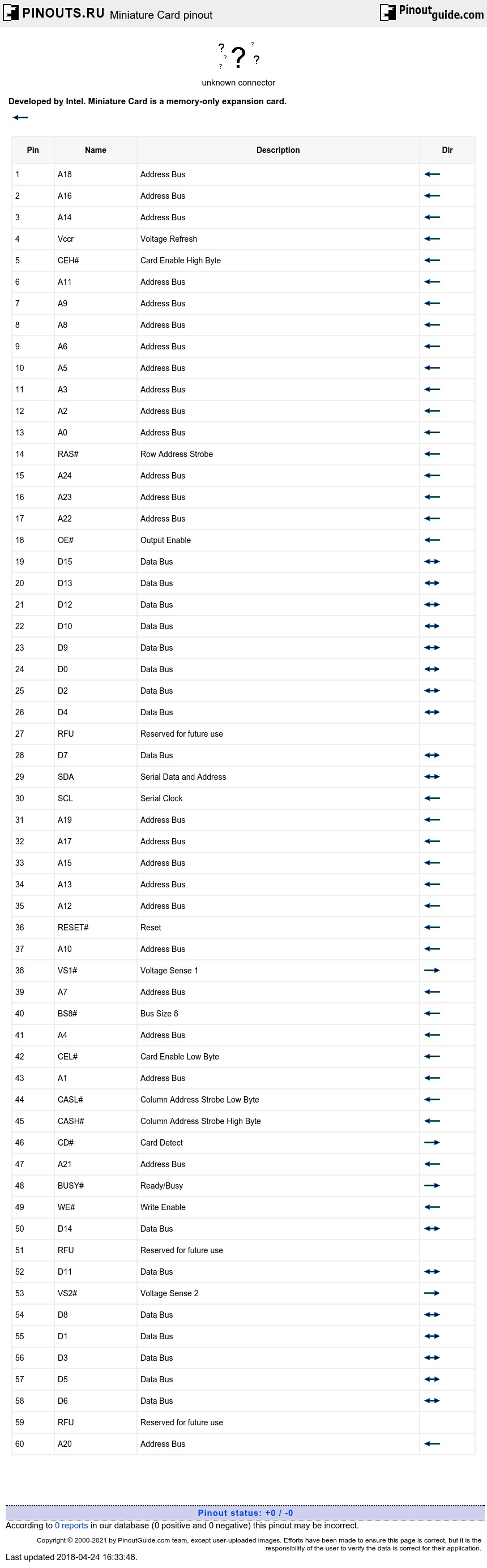

| Pin | Name | Description | Dir |

|---|---|---|---|

| 1 | A18 | Address Bus |  |

| 2 | A16 | Address Bus |  |

| 3 | A14 | Address Bus |  |

| 4 | Vccr | Voltage Refresh |  |

| 5 | CEH# | Card Enable High Byte |  |

| 6 | A11 | Address Bus |  |

| 7 | A9 | Address Bus |  |

| 8 | A8 | Address Bus |  |

| 9 | A6 | Address Bus |  |

| 10 | A5 | Address Bus |  |

| 11 | A3 | Address Bus |  |

| 12 | A2 | Address Bus |  |

| 13 | A0 | Address Bus |  |

| 14 | RAS# | Row Address Strobe |  |

| 15 | A24 | Address Bus |  |

| 16 | A23 | Address Bus |  |

| 17 | A22 | Address Bus |  |

| 18 | OE# | Output Enable |  |

| 19 | D15 | Data Bus |  |

| 20 | D13 | Data Bus |  |

| 21 | D12 | Data Bus |  |

| 22 | D10 | Data Bus |  |

| 23 | D9 | Data Bus |  |

| 24 | D0 | Data Bus |  |

| 25 | D2 | Data Bus |  |

| 26 | D4 | Data Bus |  |

| 27 | RFU | Reserved for future use | |

| 28 | D7 | Data Bus |  |

| 29 | SDA | Serial Data and Address |  |

| 30 | SCL | Serial Clock |  |

| 31 | A19 | Address Bus |  |

| 32 | A17 | Address Bus |  |

| 33 | A15 | Address Bus |  |

| 34 | A13 | Address Bus |  |

| 35 | A12 | Address Bus |  |

| 36 | RESET# | Reset |  |

| 37 | A10 | Address Bus |  |

| 38 | VS1# | Voltage Sense 1 |  |

| 39 | A7 | Address Bus |  |

| 40 | BS8# | Bus Size 8 |  |

| 41 | A4 | Address Bus |  |

| 42 | CEL# | Card Enable Low Byte |  |

| 43 | A1 | Address Bus |  |

| 44 | CASL# | Column Address Strobe Low Byte |  |

| 45 | CASH# | Column Address Strobe High Byte |  |

| 46 | CD# | Card Detect |  |

| 47 | A21 | Address Bus |  |

| 48 | BUSY# | Ready/Busy |  |

| 49 | WE# | Write Enable |  |

| 50 | D14 | Data Bus |  |

| 51 | RFU | Reserved for future use | |

| 52 | D11 | Data Bus |  |

| 53 | VS2# | Voltage Sense 2 |  |

| 54 | D8 | Data Bus |  |

| 55 | D1 | Data Bus |  |

| 56 | D3 | Data Bus |  |

| 57 | D5 | Data Bus |  |

| 58 | D6 | Data Bus |  |

| 59 | RFU | Reserved for future use | |

| 60 | A20 | Address Bus |  |

The following three is separate:

| Name | Description | Dir |

|---|---|---|

| GND | Ground | |

| VCC | Power | |

| CINS# | Card Insertion |  |

This section is currently based solely on the Miniature Card specification v1.1.

Signal Descriptions:

A0-A24

Address A0 to A24 are the address bus lines that can address up to 32 Mwords (64 MBytes). The Miniature Card specification does not require the Miniature Card to decode the upper address lines. A 2 Mbyte Miniature Card that does not decode the upper address lines would repeat its address space every 2 Mbytes. Address 0h would access the same physical location as 200000h, 400000h, 600000h, etc.

D0-D15

Data lines D0 through D15 constitute the data bus. The data bus is composed of two bytes, the low byte D[7:0] and the high byte D[15:8].

OE#

OE# indicates that the current bus cycle is a read cycle.

WE#

WE# indicates that the current bus cycle is a write cycle.

VS1#

Voltage Sense 1 signal. The card grounds this signal to indicate it can operate at 3.3 Volts. This signal must either be connected to card GND or left open.

VS2#

Voltage Sense 2 signal. The card grounds this signal to indicate it can operate at x.x Volts (the value to be determined at a later date). This signal must either be connected to card GND or left open.

CEL#

CEL# enables the low byte of the data bus (D[7:0]) on the card. This signal is not used in DRAM cards.

CEH#

CEH# enables the high byte of the data bus (D[15:8]) on the card. This signal is not used in DRAM cards.

RAS#

RAS# strobes in the row address for DRAM cards.

CASL#

CASL# strobes in the low byte column address for DRAM cards.

CASH#

CASH# strobes in the high byte column address for DRAM cards.

RESET#

RESET# controls card initialization. When RESET# transitions from a low state to a high state, the Miniature Card must reset to a predetermined state.

BUSY#

BUSY# is a signal generated by the card to indicate the status of operations within the Miniature Card. When BUSY# is high, the Miniature Card is ready to accept the next command from the host. When BUSY# is low, the Miniature Card is busy and unable to accept some data operations from the host. For example, in Flash Miniature Cards the BUSY# signal is tied to the components RY/BY# signal. However, ROM Miniature Cards would always drive BUSY# high since the host will always be able to read from a ROM Miniature Card.

Vccr

Vccr provides a low current (refresh) voltage supply. Vccr is a feature used by DRAM Miniature Cards to self-refresh during sleep mode.

SDA

I2C: Serial Data/Address.

SCL

I2C: Serial Clock are used to read the attribute information structure (AIS) from the serial EEPROM in a DRAM card.

CD#

CD# is a grounded interface signal. After a Miniature Card has been inserted, CD# will be forced low. The card detect signal is located in the center of the second row of interface signals, and should be one of the last interface signals to connect to the host. Do not confuse CD# with CINS#. CINS# is an early card detect that is one of the first signals to connect to the host.

BS8#

BS8# is a signal driven by the host to indicate if the data bus is x8 or x16. An 8-bit host must drive BS8# low and tie the high byte data bus D[15:8] to the low byte data bus D[7:0]. A 16-bit host must drive this signal high.

GND

Ground

Vcc

Vcc is used to supply power to the card.

CINS#

CINS# is a grounded signal on the front of the Miniature Card that can be used for early detection of a card insertion. CINS# makes contact on the host when the front of the card is inserted into the socket, before the interface signals connect.

Note: Direction is card relative device.

correct

correct incorrect

incorrect