VMEBus is physically based on the Eurocard sizes, mechanicals and connectors, but uses its own signalling system, which Eurocard does not define. It was first developed in 1981, and continues to see widespread use today.

In many ways the VMEbus is the pins of the 68000 run out onto a backplane. In most cases this is a bad design, because it limits you to systems similar to the chipset the bus was originally designed for. (For instance, the ISA bus is still useful only for Intel chips). However one of the key features of the 68000 was a flat 32-bit memory model, free of memory segmentation and other "anti-features". The result is that while VME is very 68000-like, the 68000 is generic enough to make this a non-issue in most cases.

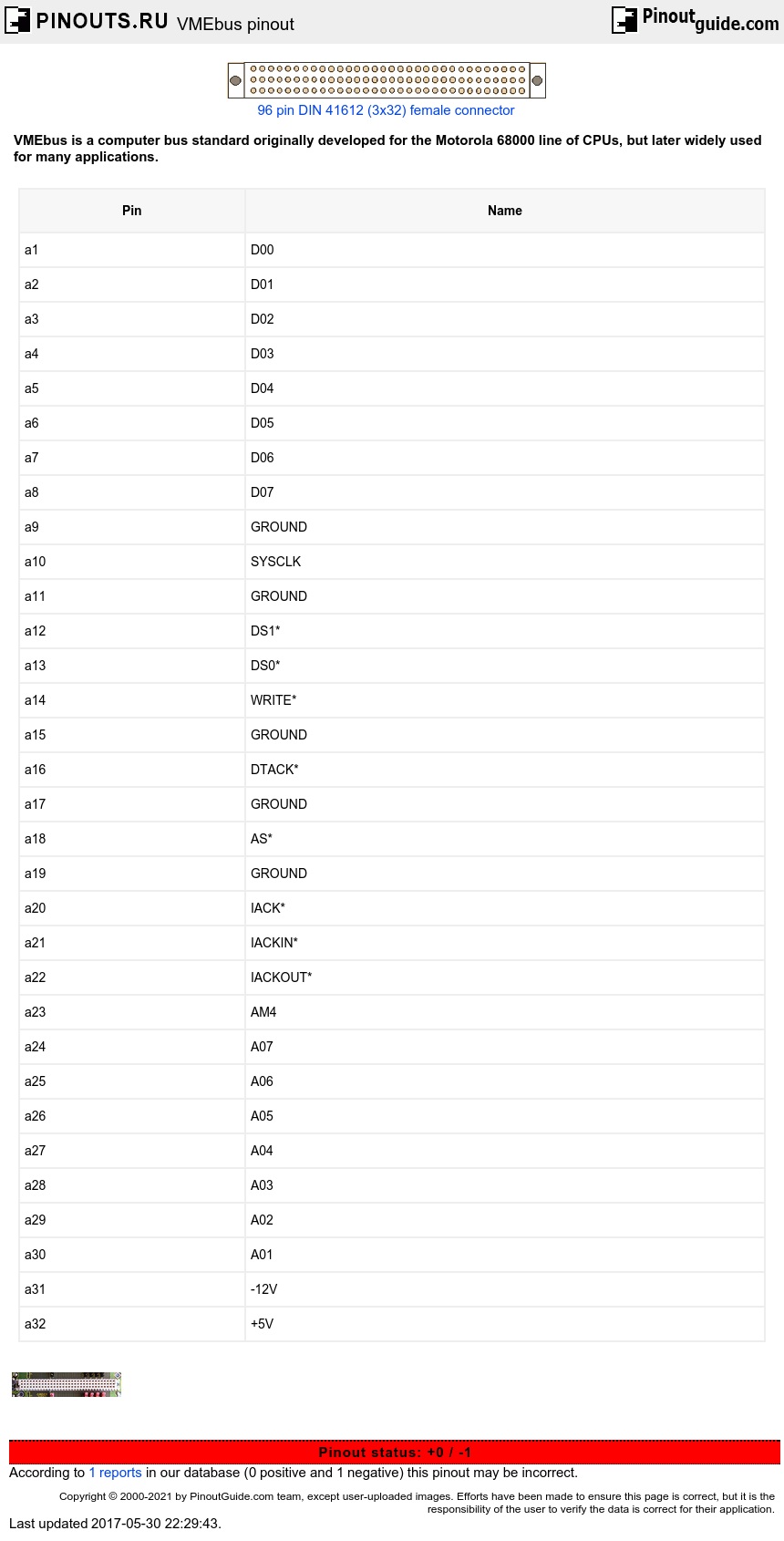

Like the 68000, VME uses separate data and address buses, both 32-bits. In the case of the 68000 the address bus was actually 24-bits and the data bus 16-bits (although it was 32/32 internally), but the designers were already looking towards full 32-bit implementations. In order to allow both widths of buses to be used, VME uses two different Eurocard connectors, the P1 and P2. P1 contains three rows of 32 pins each, implementing the first 24-bits of the address and 16-bits of the data buses, along with all of the control signals. The P2 contains one more row, which includes the remaining 8 address and 16 data pins.

In order to control the bus a set of nine lines known as the arbitration bus is used. All communications are controlled by the card inserted in slot one of the Eurocard chassis, known as the arbiter module. In general use the cards will request access to the bus by holding the bus request in lines of the arbitration bus low to indicate their slot number. When the arbiter module frees the bus it scans these lines to see if there are any held low. If so, it pulls the bus busy line low to indicate the bus is going busy again, and writes the card number back out on the bus grant out lines.

At this point the numbered card has gained access to the bus. To write data the card writes the address and data to the bus, and then pulls the address strobe line and the two data strobe lines low to indicate the data is ready, and then pulls the write pin to indicate the operation. There are two data strobes so the cards can indicate if the data is 8, 16, or 32 bits (or 64 in VME64). The card at the indicated address on the bus then reads the data and pulls the data transfer acknowledge line when it is complete (or the bus error line if need be). Reading data is essentially the same, but the controlling card places only the address on the bus and pulls the READ pin. The other card then writes the data and pulls the data strobe pins when the data is ready. This signalling scheme is asynchronous, meaning that there is no overall clock signal as there is in synchronous buses such as PCI.

VME also includes an interrupt bus, supplying all seven of the 68000"s interrupt pins. When an interrupt is supplied the arbiter module writes the interrupt level back out to the address bus to tell which interrupt is being handled. Note that there is no concept of card number in this case, because cards will often share interrupts. The excessive number of interrupt levels has often been pointed to as one of the few examples of overdesign in the 68000, and it makes even less sense in the case of a bus.

Note that in VME all transfers are DMA and every card is a master (or slave). In most bus standards there is a considerable amount of complexity added in order to support various transfer types and master/slave selection. For instance, in the ISA bus both of these features had to be added on top of the already existing "channels" model where all communications was handled by the host CPU. This makes VME considerably simpler at a conceptual level while being more powerful, although it requires somewhat more complex controllers on each card in order to work.

J=Jack (Backplane), P=Plug (Board)

P1/J1 (Required)

| Pin | Name |

|---|---|

| a1 | D00 |

| a2 | D01 |

| a3 | D02 |

| a4 | D03 |

| a5 | D04 |

| a6 | D05 |

| a7 | D06 |

| a8 | D07 |

| a9 | GROUND |

| a10 | SYSCLK |

| a11 | GROUND |

| a12 | DS1* |

| a13 | DS0* |

| a14 | WRITE* |

| a15 | GROUND |

| a16 | DTACK* |

| a17 | GROUND |

| a18 | AS* |

| a19 | GROUND |

| a20 | IACK* |

| a21 | IACKIN* |

| a22 | IACKOUT* |

| a23 | AM4 |

| a24 | A07 |

| a25 | A06 |

| a26 | A05 |

| a27 | A04 |

| a28 | A03 |

| a29 | A02 |

| a30 | A01 |

| a31 | -12V |

| a32 | +5V |

| Pin | Name |

|---|---|

| b1 | BBSY* |

| b2 | BCLR* |

| b3 | ACFAIL* |

| b4 | BG0IN* |

| b5 | BG0OUT* |

| b6 | BG1IN* |

| b7 | BG1OUT* |

| b8 | BG2IN* |

| b9 | BG2OUT* |

| b10 | BG3IN* |

| b11 | BG3OUT* |

| b12 | BR0* |

| b13 | BR1* |

| b14 | BR2* |

| b15 | BR3* |

| b16 | AM0 |

| b17 | AM1 |

| b18 | AM2 |

| b19 | AM3 |

| b20 | GROUND |

| b21 | SERCLK* |

| b22 | SERDAT* |

| b23 | GROUND |

| b24 | IRQ7* |

| b25 | IRQ6* |

| b26 | IRQ5* |

| b27 | IRQ4* |

| b28 | IRQ3* |

| b29 | IRQ2* |

| b30 | IRQ1* |

| b31 | +5V STDBY |

| b32 | +5V |

| Pin | Name |

|---|---|

| c1 | D08 |

| c2 | D09 |

| c3 | D10 |

| c4 | D11 |

| c5 | D12 |

| c6 | D13 |

| c7 | D14 |

| c8 | D15 |

| c9 | GROUND |

| c10 | SYSFAIL* |

| c11 | BERR* |

| c12 | SYSRESET* |

| c13 | LWORD* |

| c14 | AM5 |

| c15 | A23 |

| c16 | A22 |

| c17 | A21 |

| c18 | A20 |

| c19 | A19 |

| c20 | A18 |

| c21 | A17 |

| c22 | A16 |

| c23 | A15 |

| c24 | A14 |

| c25 | A13 |

| c26 | A12 |

| c27 | A11 |

| c28 | A10 |

| c29 | A09 |

| c30 | A08 |

| c31 | +12V |

| c32 | +5V |

P2/J2 (Optional)

| Pin | Name |

|---|---|

| b1 | +5v |

| b2 | GROUND |

| b3 | RESERVED |

| b4 | A24 |

| b5 | A25 |

| b6 | A26 |

| b7 | A27 |

| b8 | A28 |

| b9 | A29 |

| b10 | A30 |

| b11 | A31 |

| b12 | GROUND |

| b13 | +5V |

| b14 | D16 |

| b15 | D17 |

| b16 | D18 |

| b17 | D19 |

| b18 | D20 |

| b19 | D21 |

| b20 | D22 |

| b21 | D23 |

| b22 | GROUND |

| b23 | D24 |

| b24 | D25 |

| b25 | D26 |

| b26 | D27 |

| b27 | D28 |

| b28 | D29 |

| b29 | D30 |

| b30 | D31 |

| b31 | GROUND |

| b32 | +5V |

*) Active Low

correct

correct incorrect

incorrect